# **Table of Contents**

| 1. DESCRIPTION     |                                    |    |  |

|--------------------|------------------------------------|----|--|

|                    | 1.1 FUNCTIONAL DESCRIPTION         | 1  |  |

| 2. SPEC            | CIFICATIONS                        | 3  |  |

|                    | 2.1 PACKAGING                      | 3  |  |

|                    | 2.2 EXTERNAL COMPONENTS            | 3  |  |

|                    | 2.3 INTERNAL COMPONENTS            | 3  |  |

|                    | 2.4 CHARACTERISTICS OF THE SIGNALS | 4  |  |

|                    | 2.5 POWER REQUIREMENTS             | 4  |  |

| 3. CAMAC FUNCTIONS |                                    |    |  |

| 4. OPERATING MODE6 |                                    |    |  |

|                    | 4.1 GENERAL INFORMATION            | 6  |  |

|                    | 4.2 OPERATIONS TO BE PERFORMED     | 9  |  |

| 5. TEST            | PROCEDURE                          | 10 |  |

|                    | 5.1 INTRODUCTION                   | 10 |  |

|                    | 5.2 SUGGESTED INSTRUMENTS          | 10 |  |

|                    | 5.3 PROCEDURE                      | 10 |  |

# 1. DESCRIPTION

## 1.1 FUNCTIONAL DESCRIPTION

The CAEN Model C 469 16-CHANNEL GATE AND DELAY GENERATOR is a 1-unit wide CAMAC module provided with sixteen independent ECL differential inputs and as many outputs.

Each input signal generates a corresponding output signal after a delay interval. Both the output width (gate) and the delay interval are programmable via CAMAC in 256 equal steps (through an 8-bit digital code) within a fixed full-scale range of 500 ns with a resolution of approximately 2 ns.

The gate/delay programmed values are battery backed-up, so they remain in memory either after turning the crate off or in case of a power failure occurs.

Two module's configurations are selectable via internal dip-switches: sixteen inputs with one output per input, eight inputs with two outputs per input.

On the module's front panel:

- a standard NIM level signal with programmed delay and width, corresponding to the input selected via CAMAC, is available at each of the two "MUX" output connectors when the input itself is present.

- a standard NIM level signal sent to the "CLEAR" input connector allows the output signals to be partially or completely suppressed.

- a standard NIM level signal, with proper timing, sent to the "VETO" input connector prevents the output signals to be generated.

- a standard NIM level signal sent to the "TEST IN" input connector generates all the output signals.

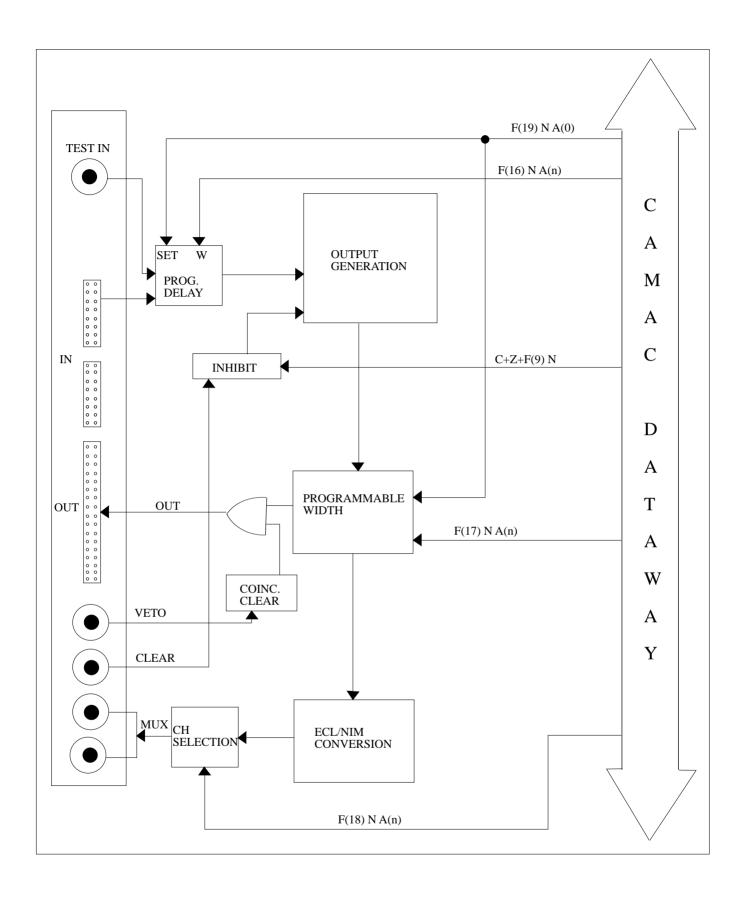

The functional block diagram of the module is shown in figure 1.

Figure 1 Block Diagram of the Mod. C 469

# 2. SPECIFICATIONS

## 2.1 PACKAGING

1-unit wide CAMAC module.

# 2.2 EXTERNAL COMPONENTS

#### **CONNECTORS:**

- No. 1 LEMO 00 type "TEST IN" . Input connector of the TEST signal (Std. NIM level).

- No. 1 2x8 pin flat cable type "IN (0..7)". Input connector (inputs 0 to 7) (Std. ECL differential level).

- No. 1 2x8 pin flat cable type "IN (8..15)". Input connector (inputs 8 to 15) (Std. ECL differential level).

- No. 1 2x16 pin flat cable type "OUT 0..15". Output connector (outputs 0 to 15) (Std. ECL differential level).

- No. 1 LEMO 00 type "VETO". Input connector of the VETO signal (Std. NIM level).

- No. 1 LEMO 00 type "CLR". Input connector of the CLEAR signal (Std. NIM level).

- No. 2 LEMO 00 type "MUX". Parallel output connectors of the Std. NIM level signal corresponding to the input selected via CAMAC.

#### **DISPLAYS:**

- No. 16 red LEDs signalling, when alight, the presence of the corresponding input signals.

- No. 1 "M". Green LED. It lights up if the module is set to the single input-single output configuration.

## 2.3 INTERNAL COMPONENTS

#### JUMPERS:

No. 2 "SW2". These dip-switches are dedicated to the selection of the module's configuration.

# 2.4 CHARACTERISTICS OF THE SIGNALS

## **INPUT**

- 0 to 15 inputs:

- Std. ECL differential level, 110 Ohm impedance.

- Min. width: 3.5 ns (10 ns to light up the red LED).

- TEST IN, CLEAR:

- Std. NIM level, 50 Ohm impedance.

- Min. width: 3.5 ns

- CLEAR to OUT delay: 10ns.

#### -VETO:

- Std. NIM level, 50 Ohm impedance.

- Min. width: 12 ns. It must precede the relative gate signal by at least 13 ns.

#### **OUTPUT**

- 0 to 15 outputs:

- Std. ECL differential level on 110 Ohm impedance.

- Rise/fall time: <3 ns.

- Multiplexed outputs ("MUX" connectors):

- standard NIM level on 50 Ohm impedance. When only one output is used, the unused connector must be terminated into 50 Ohm.

# 2.5 POWER REQUIREMENTS

+6 V 1.5 A

-6 V 2.8 A

# 3. CAMAC FUNCTIONS

| F(16) N A(n) | Writes the delay time (W1W8) of the output selected by subaddress. <b>n</b> =015. The same output is associated with the two multiplexed outputs ("MUX"). |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| F(17) N A(n) | Writes the gate width (W1W8) of the output selected by subaddress. $n=015$ . The same output is associated with the two multplexed outputs ("MUX").       |

| F(18) N A(n) | Selects the output to be associated with the two multiplexed outputs ("MUX") of the module connectors. <b>n</b> =015.                                     |

| F(19) N A(0) | Assigns the set gate and delay values to the corresponding outputs.                                                                                       |

| F(25) N A(0) | Generates a TEST signal.                                                                                                                                  |

| F(9) N       | Resets the module at S1 time.                                                                                                                             |

| C, Z         | Resets the module at S2 time.                                                                                                                             |

$^\prime$  X and Q response for each valid function  $^*$

<sup>\*</sup> modified on the 5th of February 1993

# 4. OPERATING MODE

## 4.1 GENERAL INFORMATION

The CAEN Model C 469 is a gate and delay generator provided with sixteen independent channels.

Each channel can be programmed via CAMAC with different gate widths and delay times. Up to 256 gate/delay values are selectable (through an 8-bit digital code) up to a fixed full-scale value of 500 ns, with a resolution of approximately 2 ns.

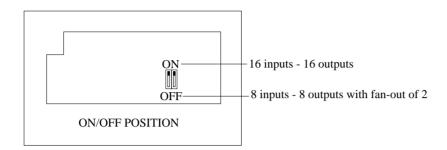

Two internal dip-switches, marked "SW2" on the printed-circuit board, allow two configurations of the module's channels:

- sixteen inputs with one output per input. This configuration gives the following input-to-output correspondence: IN0->OUT0, IN1->OUT1,..., IN15->OUT15;

- eight inputs with two outputs per input. This configuration gives the following input-to-output correspondence: IN0->OUT0 & OUT8, IN1->OUT1 &OUT9...., IN7->OUT7 & OUT15.

A standard NIM level signal sent to the "VETO" front panel connector inhibits the output gates which have the leading edge inside the VETO itself.

A standard NIM level signal sent to the "CLR" front panel connector resets each channel, therefore interrupts all the gates and all the delays present on the outputs.

During the module's operation, a standard NIM level signal, corresponding to the input selected via CAMAC (through the appropriate CAMAC function), is available at each of the two "MUX" output connectors when the input itself is present.

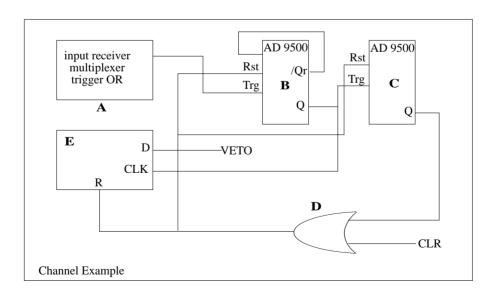

The delay and the gate width for each channel are obtained by two AD 9500s which are programmable delay generators (see the following diagram).

Due to the electrical connections adopted and keeping account of the characteristics of the AD9500 the user can obtain Td delays

$$Td = (15 + 12\% Full Scale + tdp) ns$$

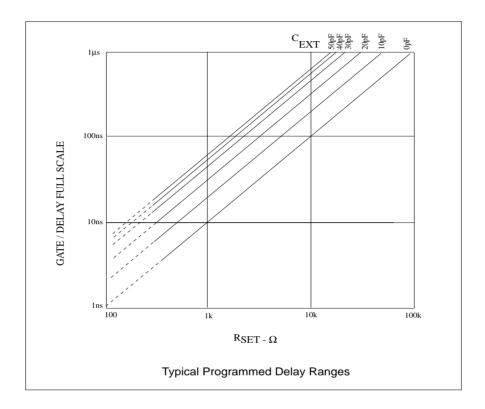

where tdp is the programmed delay value and the Full Scale depends on the value of an Rset and a Cext (see diagram below)

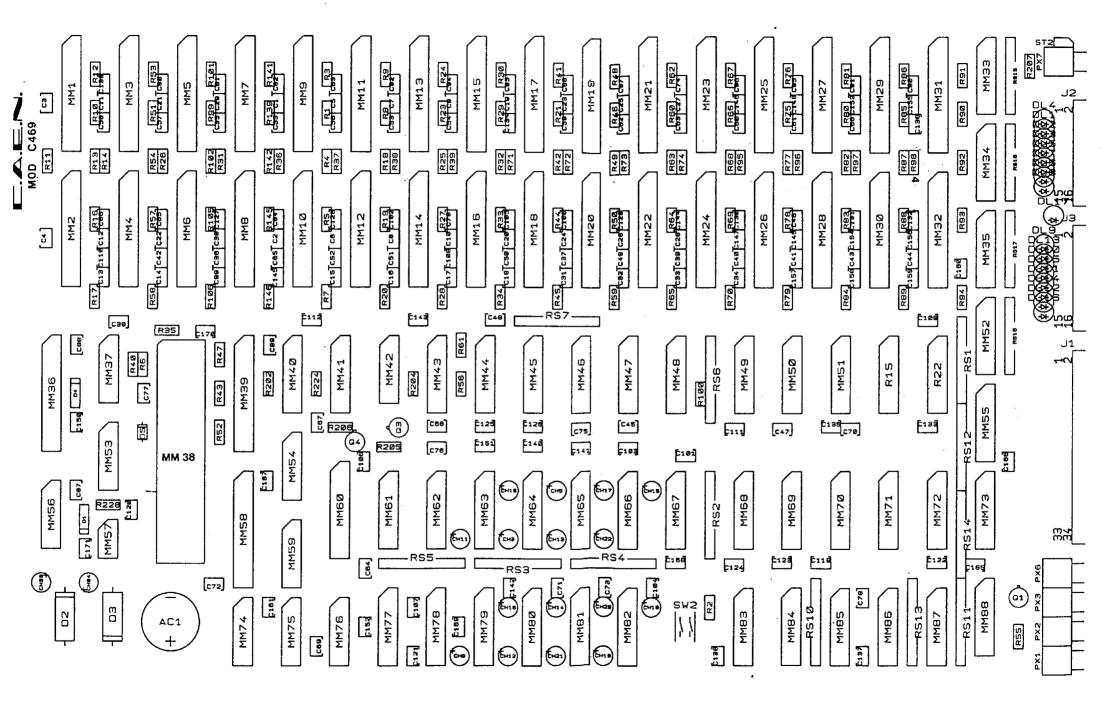

The RSET and CEXT positions on the printed circuit board are reported in the figure over the page, for each channel.

Therefore by programming a tpd = 0 the user can obtain a minimum delay of:

In the same way the user can obtain the gate time Tg:

$$Tg = (10 + 12\% Full Scale + tgp)$$

ns

where tgp is the programmed gate width value).

For each channel, the time Ti between two consecutive input pulses in order to minimise the error on Tg and Td must be:

Ti = 1.5 Tm (where Tm is the highest value between Tg and Td).

In this way the user can obtain errors less than 1% of the programmed values.

# 4.2 OPERATIONS TO BE PERFORMED

CAUTION: before inserting or removing the module, turn the CAMAC crate OFF.

**PRELIMINARY**: configure the module's channels as required by setting the SW2 dip-switches to the ON or OFF position (see figure below). Both the switches must be either on or off.

At power on, the green LED "M" lights up if the module is set to the single input-single output configuration.

- 1. Insert the C 469 module into the CAMAC crate, then turn the crate itself ON.

- 2. Connect the used channels to the corresponding input and output devices.

If only one of the two "MUX" connectors is used, terminate the other one into 50 Ohm.

- 3. For each channel to be used, perform the following operations:

- (a) By performing an F(16) N A(n) CAMAC function (where n=channel number), set the required delay time value (W1..W8): X response is given.

- (b) By performing an F(17) N A(n) CAMAC function (where n=channel number), set the required gate width value (W1..W8): X response is given.

- 4. By performing an F(18) N A(n) CAMAC function (where n=channel number), select the channel to be multiplexed at the two "MUX" connectors: X response is given.

- 5. Perform an F(19) N A(0) CAMAC function: each set value is assigned to the corresponding channel. X response is given.

- 6. Turn the input and output devices ON: the presence of an input signal is signalled by the corresponding red LED (ON=signal presence, OFF=signal absence).

All settings are battery backed-up, so the module does not have to be reprogrammed after a power failure: in this case, only an F(19) N A(0) CAMAC function has to be performed to reassign each stored value to the relevant channel.

# 5. TEST PROCEDURE

## 5.1 INTRODUCTION

The operations to be performed to test the C 469 module are listed in the procedure below and have to be carried out according to their numerical sequence. None of the procedural step can be omitted.

Each procedural step contains the operation to be performed and the corresponding effect or the verification to be accomplished.

## **5.2 SUGGESTED INSTRUMENTS**

- No. 1 Oscilloscope.

- No. 1 Signal Generator capable of producing standard NIM level signals on 50 Ohm impedance.

- No. 1 CAMAC crate provided with a manual controller (model: CAEN C 249).

## **5.3 PROCEDURE**

The C 469 module comes from CAEN fully tested and calibrated. This procedure allows the user to accomplish a functional test of the module.

**CAUTION:** before inserting or removing the module, turn the crate OFF.

- 1. On the module's printed-circuit board, switch on the two internal switches "SW2": the module is set to the single input-single output configuration.

- 1. Insert the module into the crate.

- 2. Turn the crate ON: the green LED "M" lights up.

- 3. For each channel, using a fixed value of gate width and delay time for all the channels, perform the following operations:

- (a) By performing an F(16) N A(n) CAMAC function (where n=channel number), set the delay time value (W1..W8): X response is given.

- (b) By performing an F(17) N A(n) CAMAC function (where n=channel number), set the gate width value (W1..W8): X response is given.

- 4. By performing an F(18) N A(n) CAMAC function (where n=channel number), select the channel to be multiplexed at the two "MUX" connectors: X response is given.

- 5. Perform an F(19) N A(0) CAMAC function: each set value is assigned to the corresponding channel. X response is given.

- 6. Send a standard NIM level signal to the "TEST IN" front panel connector.

(All the inputs must be at false ECL logic level

- 7. With the Oscilloscope, verify that:

- (a) each output signal ("OUT" connector) has the programmed delay time and gate width:

- (b) a standard NIM level signal is present at each of the "MUX" connectors.

- 8. Remove the signal cable from the "TEST IN" connector.

- 9. Perform an F(25) N A(0) CAMAC function cyclically.

- 10. Repeat step 7..

- 11. Switch the crate OFF, then turn it ON.

- 12. Perform an F(19) N A(0) CAMAC function: each stored value is reassigned to the corre sponding channel. X response is given.

- 13. Perform an F(25) N A(0) CAMAC function cyclically.

- 14. Repeat step 7.

- 15. Send a standard NIM level pulse-train signal to the "CLR" connector in such a way that each pulse is present during the channels' programmed delay: with the Oscilloscope, verify that no signal is present both at the "OUT" connector and at the "MUX" ones.

- 16. Remove the signal cable from the "CLR" connector and connect it to the "VETO" connector: with the Oscilloscope, verify that all the signals are present both at the "OUT" connector and at the "MUX" ones.

- 17. Send a standard NIM level pulse-train signal to the "VETO" connector in such a way that each pulse is present during the channels' programmed gate: with the Oscilloscope, verify that the output signals are false when the input pulses are true.

- 18. Switch the crate OFF, remove the signal cable from the "VETO" connector then remove the module from the crate.

- 19. On the module's printed-circuit board, set the SW2 dip-switches to the OFF position: the module is set to the eight-inputs-with-two-output-per-input configuration.

- 20. Insert the module into the crate, then turn the crate ON: the green LED "M" is OFF.

- 21. Repeat step 12.

- 22. Repeat steps 6. to 18..

THE MODULE IS TESTED AND OPERATES CORRECTLY