# SIS3820 VME Scaler

# User Manual

SIS GmbH Harksheider Str. 102A 22399 Hamburg Germany

Phone: ++49 (0) 40 60 87 305 0 Fax: ++49 (0) 40 60 87 305 20

email: info@struck.de http://www.struck.de

Version: sis3820-M-0-001-v183-scaler as of 20.11.06

# Revision Table:

| Revision | Date     | Modification                                            |  |

|----------|----------|---------------------------------------------------------|--|

| 0.0x     | 13.02.02 | Start of module definition                              |  |

| 0.10     | 23.06.03 | Prerelease                                              |  |

| 1.00     | 24.06.03 | First official release                                  |  |

| 1.01     | 11.08.03 | Id. reg $R/W \rightarrow R$ only                        |  |

|          |          | bug fix in JTAG JP570 text and watchdog enable          |  |

| 1.10     | 09.12.03 | VME JTAG firmware upgrade support,                      |  |

|          |          | read during preset scaler operation, support for 512 MB |  |

|          |          | memory strips and add mode                              |  |

|          |          | (Xilinx Firmware: sis38200102.mcs)                      |  |

| 1.20     | 27.04.04 | Firmware Version 01 03                                  |  |

|          |          | Chained Block Transfer (CBLT) implemented               |  |

|          |          | (Xilinx Firmware: sis38200103.mcs)                      |  |

| 1.30     | 04.06.04 | Firmware Version 01 04                                  |  |

|          |          | 48-bit deep counter implementation in channels 1 and 17 |  |

|          |          | (for scaler mode, new address 0x210)                    |  |

| 1.31     | 09.11.04 | Bug fix in address map, change FIFO threshold register  |  |

|          |          | explanation                                             |  |

| 1.32     | 13.01.05 | Couple of index entries added, typo fix                 |  |

| 1.40     | 20.05.05 | Firmware Version 01 05                                  |  |

|          |          | New Control Output mode 2 (10Mhz)                       |  |

| 1.50     | 26.08.05 | Firmware Version 01 08                                  |  |

|          |          | New Control Input mode 6 (with external counter clear)  |  |

| 1.60     | 14.10.05 | Firmware Version 01 09                                  |  |

|          |          | Bug fix in control input inversion                      |  |

|          |          | New register 0x214 (veto external count inhibit)        |  |

| 1.61     | 20.10.05 | Bug fix in example veto external count register         |  |

| 1.70     | 03.11.05 | Firmware Version 01 0A                                  |  |

|          |          | New register 0x218 (test pulse mask register)           |  |

| 1.71     | 04.12.05 | Bug fixes                                               |  |

| 1.72     | 11.02.06 | ESD note added                                          |  |

| 1.80     | 15.06.06 | New MUX_OUT feature, firmware revision 0xB              |  |

| 1.81     | 19.06.06 | Bug fixes                                               |  |

| 1.82     | 25.10.06 | Note on external LNE/channel N rate being limited to 5  |  |

|          |          | MHz                                                     |  |

| 1.83     | 21.11.06 | JTAG jumper JP570 factory default                       |  |

# **1** Table of contents

| 1 | Table of contents                                                                                                      | 3    |

|---|------------------------------------------------------------------------------------------------------------------------|------|

| 2 | Introduction                                                                                                           | 7    |

| 3 | Technical Properties/Features                                                                                          | 8    |

| 4 | Functionality                                                                                                          |      |

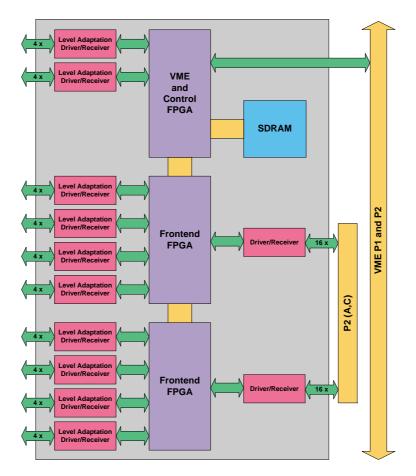

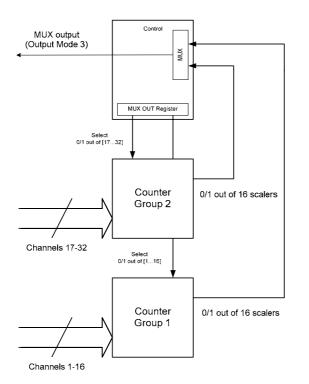

| - | 4.1 Block Diagram                                                                                                      |      |

|   | 4.2 Modes of operation                                                                                                 |      |

|   | 4.2.1 Scaler/Counter                                                                                                   |      |

|   | 4.2.2 Latching Scaler                                                                                                  |      |

|   | 4.2.3 Preset Scaler                                                                                                    |      |

|   | 4.2.4 Multi channel Scaler (MCS)                                                                                       | . 10 |

|   | 4.2.5 Histogramming Scaler(3820 01 02 and higher design)                                                               | . 10 |

| 5 | Getting started                                                                                                        | 11   |

|   | 5.1 Installation                                                                                                       | . 11 |

|   | 5.2 LINUX example/test code                                                                                            | . 11 |

|   | 5.2.1 User LED test                                                                                                    |      |

|   | 5.2.2 Readout of Module Id. and firmware revision register                                                             |      |

|   | 5.2.3 Standard Counter                                                                                                 |      |

|   | 5.2.4 Multiscaler (MCS)                                                                                                |      |

|   | 5.2.5 Preset Scaler                                                                                                    |      |

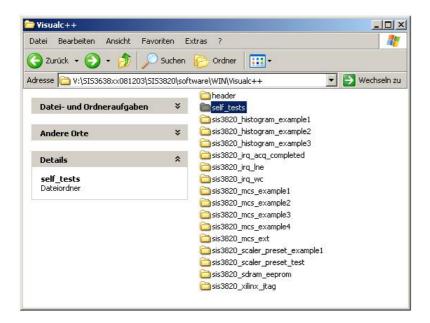

|   | 5.3 Win2K/XP Visual C++ example/test code                                                                              |      |

| 6 | VME Addressing                                                                                                         |      |

|   | 6.1 Address map                                                                                                        |      |

| 7 | Register description                                                                                                   | 18   |

|   | 7.1 Control/Status Register(0x, write/read)                                                                            |      |

|   | 7.1.1 Counter test mode                                                                                                |      |

|   | 7.1.2 25 MHz test pulse mode                                                                                           |      |

|   | 7.1.3 Reference pulser channel 1                                                                                       |      |

|   | 7.2 Module Id. and Firmware Revision Register (0x4, read)                                                              |      |

|   | 7.2.1 Major revision numbers                                                                                           |      |

|   | 7.3 Interrupt configuration register (0x8)                                                                             |      |

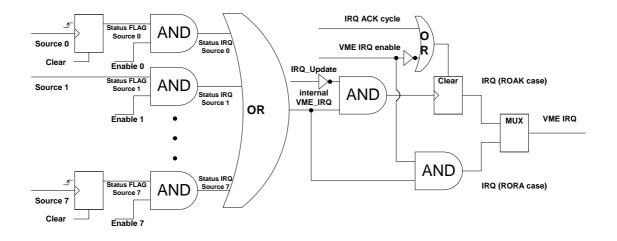

|   | 7.3.1 IRQ mode                                                                                                         |      |

|   | 7.4 Interrupt Control/Status register (0xC)                                                                            |      |

|   | 7.4.1 Interrupt sources                                                                                                |      |

|   | 7.5 (0x10)Acquisition preset register                                                                                  |      |

|   | <ul> <li>7.6 Acquisition count register (0x14)</li> <li>7.7 LNE Prescaler factor register (0x18)</li> </ul>            |      |

|   | <ul> <li>7.7 LNE Prescaler factor register (0x18)</li> <li>7.8 Preset value register counter group 1 (0x20)</li> </ul> |      |

|   | <ul> <li>7.8 Preset value register counter group 1 (0x20)</li></ul>                                                    |      |

|   | <ul> <li>7.10 Preset Enable and Hit register (0x28)</li></ul>                                                          |      |

|   | 7.11 CBLT/Broadcast setup register                                                                                     |      |

|   | 7.12 SDRAM page register (0x34)                                                                                        |      |

|   | <ul> <li>7.13 FIFO word counter/memory address pointer register (0x38)</li> </ul>                                      |      |

|   | 7.14 FIFO word counter threshold (0x3C)                                                                                |      |

|   | 7.15 HISCAL_START_PRESET register (0x40)                                                                               |      |

|   | 7.16 HISCAL_START_COUNTER register (0x44)                                                                              |      |

|   | 7.17 HISCAL_LAST_ACQ_COUNTER register (0x48)                                                                           | . 23 |

|   | 7.18 (Acquisition) Operation Mode register (0x100)                                                                     | . 23 |

|   | 7.18.1 Modes of Operation modes (Bits 30:28)                                                                           | . 23 |

|   | 7.18.2 Input modes (Bits 18:16)                                                                                        |      |

|   | 7.18.3 Output mode (Bits 21:20)                                                                                        |      |

|   | 7.18.4 HISCAL_START_SOURCE_BIT (Bit 14)                                                                                |      |

|   | 7.18.5 SDRAM mode (Bit 12) and SDRAM add mode (Bit 13)                                                                 |      |

|   | 7.18.6 Arm/enable source                                                                                               |      |

|   | 7.18.7 LNE source                                                                                                      |      |

|   | 7.18.8 Data format                                                                                                     | . 23 |

# SIS3820 VME Scaler

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.19 Copy disable register (0x104)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.20 LNE channel select register (0x108)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.21 PRESET channel select register (0x10C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

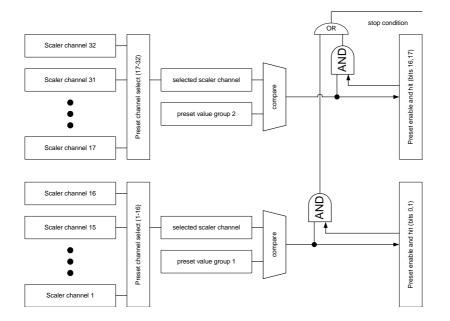

| 7.21.1 Preset scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.22 MUX OUT channel select register (0x110)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7.23 Inhibit/count disable register (0x200)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7.24 Counter clear register (0x204)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7.25 Counter Overflow register (0x208)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.26 Channel 1/17 Bits 33-48 register (0x210)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.27 Veto external count inhibit register (0x214)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.28 Test pulse mask register (0x218)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.29 SDRAM SPD register (0x300)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.30 JTAG_TEST register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.31 JTAG_DATA_IN register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.32 JTAG_CONTROL register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.33 One wire Id. register (tbd)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.34 FIFO address space (0x800000-0xFFFFC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.34.1 non incrementing VME master                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.34.2 incrementing VME master                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.35 SDRAM address space (0x800000-0xFFFFC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8 Data Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8.1 32-bit Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8.2 24-bit Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8.3 16-bit Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8.4 8-bit Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9 Front panel elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

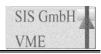

| 9.1 Front Panel Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9.2 Front Panel LEDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9.3 Flat cable Input/Output Pin Assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

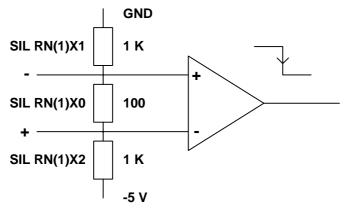

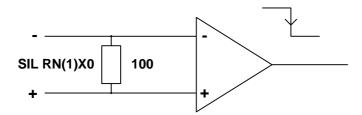

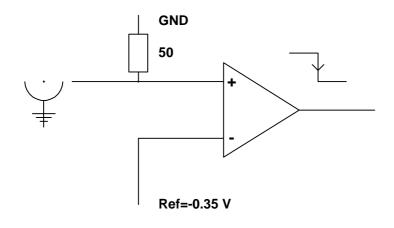

| 9.3       Flat cable Input/Output Pin Assignments.         9.3.1       ECL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

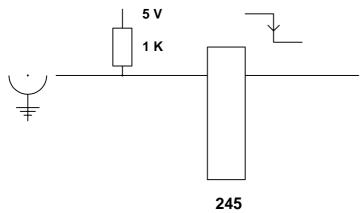

| 9.3.1 ECL<br>9.3.2 TTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23<br>23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

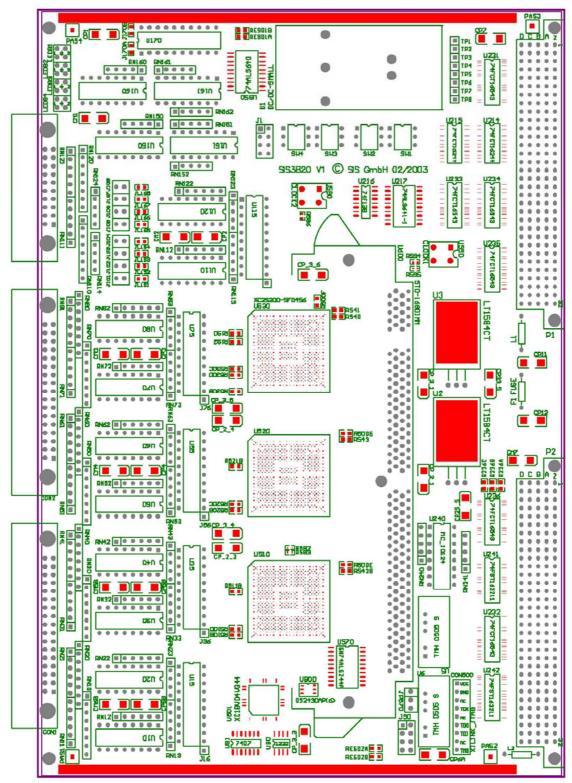

| 9.3.1 ECL<br>9.3.2 TTL<br>10 Board Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23<br>23<br>23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 9.3.1       ECL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23<br>23<br>23<br>23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 9.3.1 ECL<br>9.3.2 TTL<br>10 Board Layout<br>11 Jumper settings/pinouts<br>11.1 J1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23<br>23<br>23<br>23<br>23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9.3.1       ECL         9.3.2       TTL         10       Board Layout         11       Jumper settings/pinouts         11.1       J1         11.2       J90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23<br>23<br>23<br>23<br>23<br>23<br>23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9.3.1       ECL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9.3.1       ECL         9.3.2       TTL         10       Board Layout         11       Jumper settings/pinouts         11.1       J1         11.2       J90         11.3       JP570 JTAG source         11.4       CON500 JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 9.3.1       ECL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |